In my last post I said I was going to integrate the write cache into my two-way cache *before* adding it to the Minimig core – but I got impatient!

This is running on the Turbo Chameleon 64. No binaries yet, but the code is checked into the repo at https://github.com/robinsonb5/minimig_tc64/tree/constraints

Some more benchmarks from AIBB follow: These are all relative to A3000/25 with 68020 instructions:

| Test | Docking13 | Two Way Cache |

| EmuTest | 1.13 | 1.27 |

| WritePixel | 0.5 | 0.53 |

| Sieve | 0.72 | 0.92 |

| Dhrystone | 0.88 | 1.13 |

| Sort | 0.78 | 1.19 |

| Matrix | 0.66 | 0.81 |

| IMath | 1.26 | 1.37 |

| MemTest | 0.63 | 0.59 |

| TGTest | 0.7 | 0.73 |

| Savage | 1.37 | 1.43 |

| Beachball | 1.22 | 1.36 |

| CplxTest | 0.95 | 1.04 |

| TranTest | 1.32 | 1.38 |

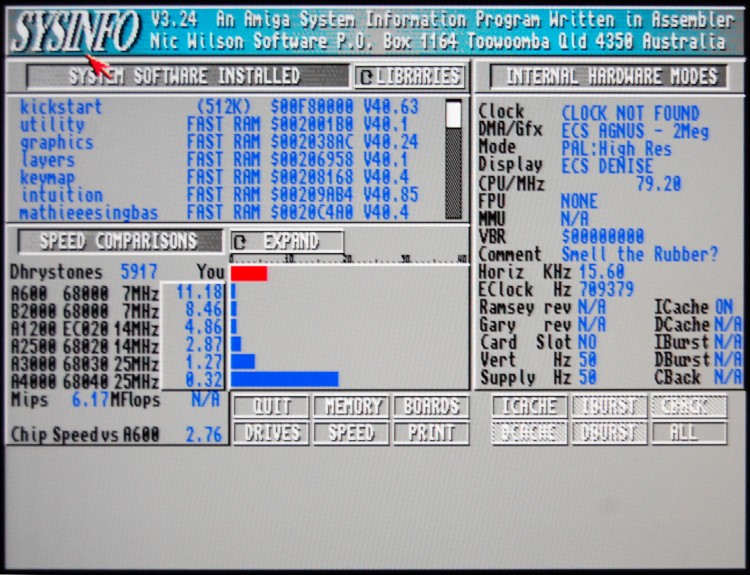

So while SysInfo reports a 40% speedup, the more “real-world” tests in AIBB suggest an average speedup of about 16%. Interestingly, the “memtest” test is slower now.

There are a number of things still to be done which should improve this further:

- Currently writes aren’t cached at all unless the target location is already in cache due to a read. Either way, the CPU has to wait until the SDRAM cycle’s finished. The simplistic write cache from the TG68MiniSOC project would allow the CPU to continue immediately after dispatching the write, and can gang writes from a single burst together, greatly increasing the speed of longword writes.

- The read phase of the Two Way Cache could be more efficient – can probably save at least one, possibly two cycles.

- The core still doesn’t use bank interleaving. This would allow one bank to be devoted entirely to Chip RAM, Kickstart ROM and OSD RAM, with the other three banks providing 24 meg of true Fast RAM that’s never slowed by accesses to the first bank.