In my previous post I talked about FPGAs and the Minimig project. One of the platforms that has received a port of Minimig is the Altera/Terasic DE1 FPGA development board. This is a nice little board which comes with a Cyclone 2 FPGA, 8 meg of SDRAM, some SRAM, some flash and a controller chip to configure the FPGA at power-on. It also has an SD card slot, PS/2 keyboard port, VGA out, an RS232 serial port, an audio codec, some switches, LEDs and a couple of 40-pin general purpose IO headers.

The one downside to this board is that the FPGA is a bit poky, with only about 20,000 logic elements – only just enough to hold the Minimig design, and not large enough to hold the latest 68020 version of the TG68 softcore.

The original DE1 port of Minimig can be found here, while a fork which will hopefully see some new developments in the future can be found here. Binaries are available, and also complete source if anyone’s else is interested in playing with it.

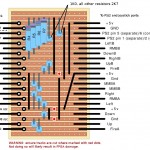

While the DE1 board has a PS/2 keyboard port, there’s no mouse port and (unsurprisingly!) no DB9 joystick ports – so these need to be added via an extra board connected to one of the GPIO headers. The source archives contain a suitable schematic, but since my circuit creation skills don’t yet extend beyond stripboard, I made a stripboard layout for the extra board. The layout and a couple of photos of the completed board appear below:

Hi,

I’ve been working on a m68k machine recently (I have it simulated in software, I’ve only recently started working on the real hardware). Your example project was pretty useful for getting TG68 up and running. Do you know where I can grab the latest source for TG68? The “official” opencores page looks out of date. Have you had any issues with it so far? I’m having major issues getting it to write to the PSRAM on my Nexys2 board :(.

Cheers,

Daniel

The nearest thing to an “official” up-to-date TG68 release that I’m aware of is Christian Vogelgsang’s Chameleon64 Minimig github repo: https://github.com/cnvogelg/minimig_tc64 (of which my own is a fork).

I haven’t yet had the opportunity to try PSRAM, but I’ve just got hold of an LPRP board which I think has PSRAM, so I’ll have a play with that one of these days.

As for figuring out where your RAM problem lies, I’d suggest looking into whatever is the Xilinx equivalent of SignalTap – I wouldn’t have been able to get my own TG68 project working without SignalTap.

Xilinx’s equivalent of SignalTap is ChipScope.. which seems to be $600 for the cheapest license. 🙁

I have built up a board with some leds etc so I can see all of the bus strobes, data and address (and a standard UART which will be doing the hello world thing once it works well enough to run the startup code and jump into C :)). I’m just waiting on some more 7 seg displays to come to display the address bus.. waiting on components from China is painful.

Thanks for the info :).

Ouch! Yeah I read that the Xilinx web pack doesn’t have the SignalTap equivalent. Shame.

Have you considered picking up a cheap EP2C5 board on EBay? You can get one with USB blaster JTAG cable for under $50 delivered. Only a small FPGA – not big enough to hold the new TG68 and do anything useful with it – but more than large enough to monitor external signals with SignalTap, or even masquerade as a small RAM for testing purposes.

I don’t really have the money to get another FPGA board at the moment. I do want a bigger FPGA at some point.

I almost have it going now though.. I had some mistakes in the m68k asm I wrote to test and it seems my clock needs to be a lot faster than 1hz to meet the timing requirements for the PSRAM. 🙂

I actually have 6 or so 68SEC000 in my parts box.. I have some really fast SRAMs, CPLDs for glue logic etc. I’m putting off building up that hardware until I can verify that my video, dma etc are actually possible to implement. If I had enough IO’s I would just hook up a real 68k 🙂