Anyone remember CU Amiga Magazine’s “ProjectXG”? This was a DIY project they ran, based on a hack that was published on Aminet, to interface a Waveblaster MIDI daughterboard to the Amiga’s serial port, to provide a pretty good quality MIDI tone module.

The daughterboard most commonly used for this project was Yamaha’s DB50XG, though any card which attached to a “Waveblaster” header could be used. (Googling Waveblaster now, however, will find you a Yamaha product of quite a different nature.)

The DB50XG’s successor, the DB60XG was manufactured under license by NEC as the XR385, and this seems to be the easiest such card to find these days. It’s very similar to the DB50XG, it just has some very subtly different voicing, and can apply its DSP effects to incoming audio as well as its own sounds.

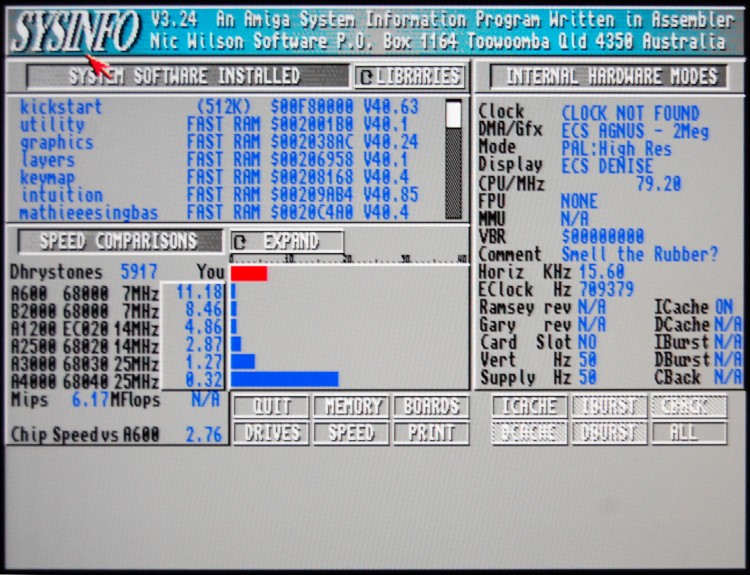

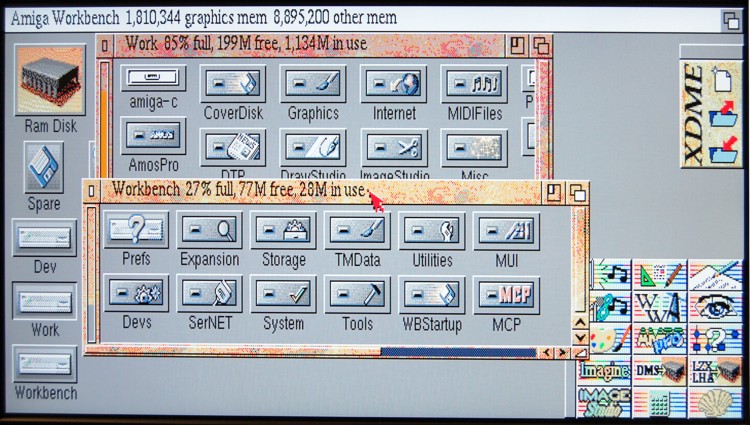

Having built a ProjectXG many years ago, then selling it a year or so back and promptly building another one, I naturally wanted to interface a Waveblaster card to one of my Minimig variants, and listen to some old MIDI files again.

Continue reading